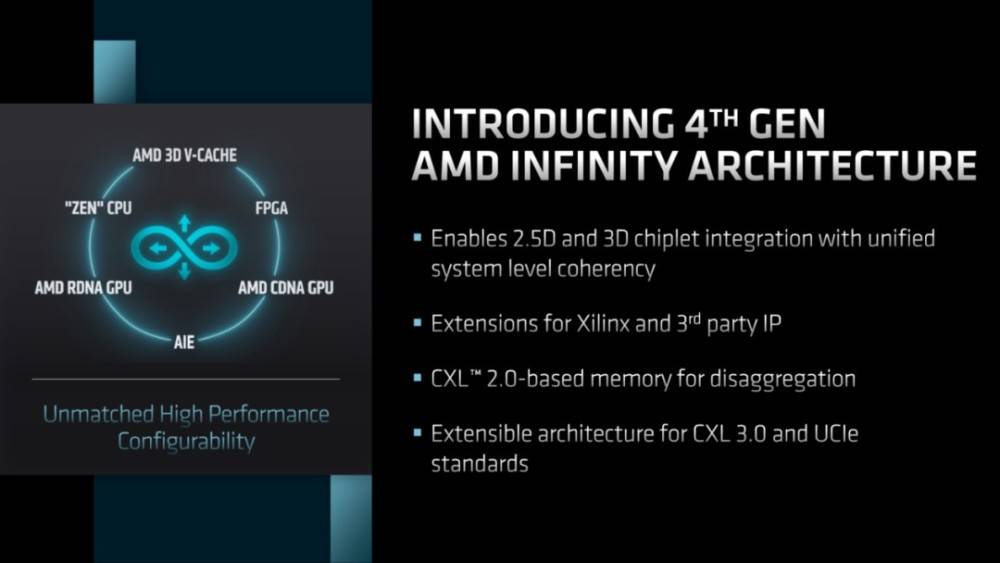

近日,AMD公布其最新CPU与GPU路线图,除了新工艺与新架构信息,先进封装技术无疑是新路线图中最值得关注的内容。无论是CPU、GPU、FPGA,还是多核异构集成产品,采用Chiplet(芯粒,也被译作“小芯片”)实现已经成为AMD主流产品的标配。当前,AMD在量产的Chiplet工艺集成的标准产品超过40个。

(来源: AMD)

在路线图中,AMD也将其Chiplet间互连的无限架构(Infinity Architecture)升级到第四代。在第四代无限架构中,AMD加入Xilinx IP与第三方IP的支持,并预留了支持CXL 3.0与UCIe标准的可能。

(来源: AMD)

为什么先进封装能维系摩尔定律?

以AMD等厂商为代表,从先进封装入手来提高芯片(或可称之为芯片系统)性能,正逐渐成为业内共识,采用Chiplet等系统封装技术,在系统层面可实现性能指数型增长,并能有效控制芯片开发、制造成本,现已成为业内维系摩尔定律的主流方法。

一个典型芯片系统,性能主要取决于三个因素,即计算、存储与接口。早期主要依靠提升计算核心与存储器的时钟,就能大幅提升系统性能,随着丹纳德定律失效,单纯提升时钟速度带来的散热问题,已经难以解决,一种不再依靠高时钟速度的多核架构开始流行。

不同模块之间的接口速度,一直是系统性能提升的最大瓶颈。计算与存储接口的性能瓶颈最早被重视,由于计算核心(处理器)与存储器分属不同封装,需要通过电路板(PCB)来连接,而电路板传输性能则受到物理尺寸的严格限制,为减少电路板瓶颈给系统性能的限制,处理器和存储器在设计时就要做诸多权衡。例如,在存储器中加上成本较高的高速缓存(Cache),存储器端也有高带宽存储器(HBM),而学术界则一直在研究存算一体等新型计算架构。这些技术的设计发展思路,都是通过减少电路板对系统性能的限制,激发系统综合性能,只是在方式方法上有所不同。芯粒等先进封装技术的商业化落地,标志着通过封装技艺提升系统性能的技术日臻成熟。

封装原本是集成电路设计生产中技术含量相对较低的一环,作为电路板与裸芯片(die)之间的中介,封装在很长时间都处于产业从属地位,从业者对封装“性能”榨取有限,因而留出了在封装方向对芯片系统性能提升的巨大空间。

如前所述,电路板是系统性能限制的主要因素之一,考虑到不同整机厂商电路板设计生产能力不同,芯片厂商在开发芯片的时候不得不为可量产的整机产品而做出性能折中。芯粒技术,通过硅中介层和高性能电路板将多颗裸芯片封在一个封装中,由封装厂商或者晶圆制造厂商,提供比普通电路板性能更高的电路板基座,与普通电路板相比,封装电路基板走线较短,布线密度更高,从而可以大幅减少不同模块之间传输数据时的系统性能损失,为持续提升系统性能打开了空间。

利用芯粒技术,芯片厂商还可以将大芯片分成多个小芯片,减少芯片设计复杂度的同时,还能提高良率。芯粒技术也支持异质集成,可将不同工艺的裸芯片放入同一个封装。例如,计算核心与存储器,采用最先进的制造工艺全新设计,而接口则采用比最先进工艺早一两代的制造工艺,而模拟模块可以采用更成熟的工艺,此时接口与模拟模块均可以采用成熟IP来开发,能进一步降低成本,并可保证良率。由此可见,利用这一技术,既能打破性能提升限制,又能降低开发成本,还有助于保证量产良率,因而芯粒技术在复杂芯片开发中越来越受到重视。

横空出世的UCIe

AMD的Zen 2处理器是用芯粒技术实现异构芯片集成的代表作,该架构将IO模块和处理器核心分离成多达9个小芯片,处理器核心采用7纳米工艺制造,而IO模块采用之前成熟的14或12纳米工艺设计制造,小芯片通过AMD Infinity高速接口技术实现连接。

英特尔的Ponte Vecchio则通过Xe Link技术,将47个小芯片——英特尔称之为芯砖(Tile)——封在一起。其他厂商,英伟达有自家的片间互连技术NVLink,而苹果也用UltraFusion互连技术实现了首个集成超千亿晶体管的大芯片M1 Ultra。

可见,芯粒技术在大芯片发开中的应用已经相当普遍,不过各厂商都采用自有技术来实现互连接口,这对晶圆厂、封装厂、乃至芯片开发者以及用户而言,开发不同厂商的芯粒产品,需要重新开发对应的硅中介层或电路基板,软件也要支持相应的传输协议,这无疑是一种沉重的负担。

为将芯粒接口标准化,降低不同晶圆制造与封测厂提供芯粒基础模块的重复开发成本,给设计公司提供更多配置选择,由英特尔公司牵头,联合台积电、三星、AMD、Arm、高通、日月光、谷歌云、Meta和微软等行业巨头,组建了UCIe(Universal Chiplet Interconnect Express,通用芯粒互连技术)联盟,倡导建立一个统一的片间互连标准UCIe,以期打造一个更开放的芯粒生态联盟。

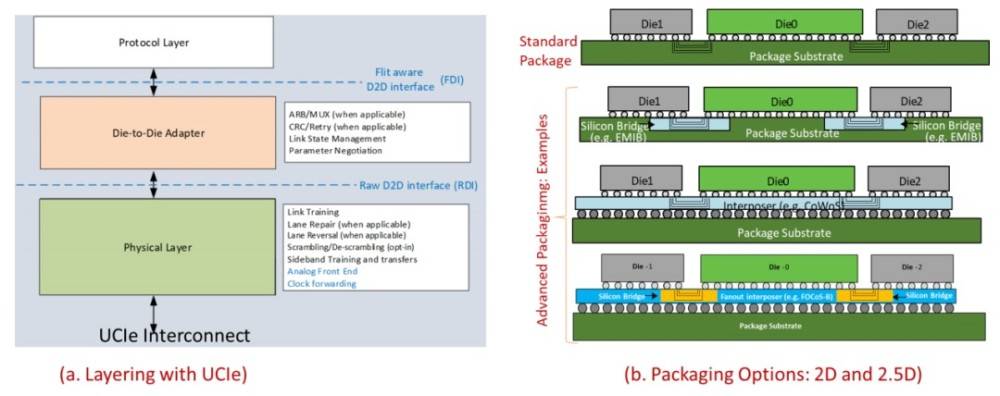

作为一个由诸多半导体、科技巨头所建立的组织,UCIe产业联盟已经推出UCIe 1.0标准,该标准是一个三层协议,如图一所示。物理层负责电信号、时钟、链路协商、边带等,裸片适配层(Die-to-Die Adapter)为芯粒提供链路状态管理和参数协商,它可选地通过循环冗余校验 (CRC)和重传机制保证数据的可靠传输,UCIe接口通过这两层与标准互连协议层相连。

UCIe架构(来源: UCIe)

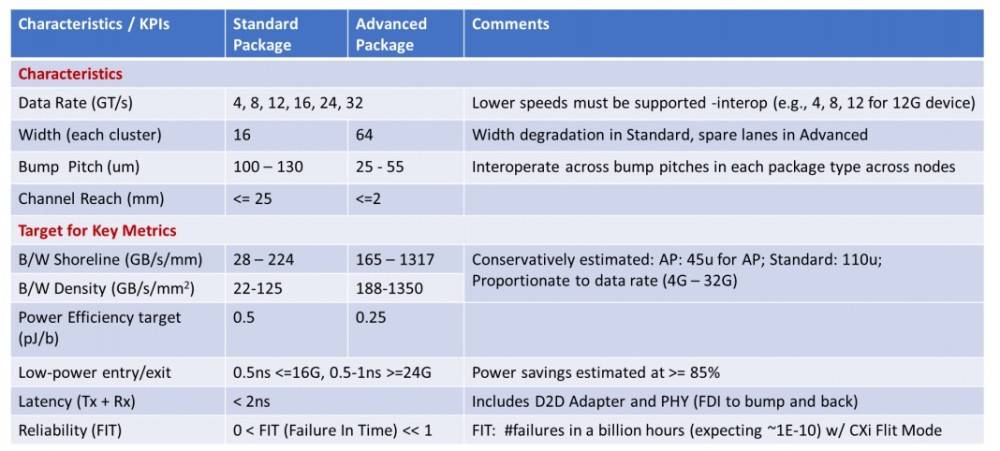

当前,UCIe 1.0、PCIe (PCI Express)和CXL (Compute Express Link)等标准,虽然都为高速互连定制,但UCIe既支持封装内集成,也支持封装间互连,可用于数据中心等大型系统设备间的互连组装。对封装内互连,UCIe既支持成本优先的普通封装,也支持能效或性能优先的先进封装。UCIe 1.0的具体技术指标如下表所示。

UCIe主要技术参数(来源: UCIe)

由UCIe 1.0协议看来,协议层的设计通过不同模式支持PCIe 5.0、PCIe 6.0、CXL 2.0和CXL 3.0等多种标准,注重接口协议上的兼容性和互操作性,对传输速率的支持也预留了升级的空间。裸片适配层的设计在保证数据可靠传输的同时,兼顾了成本和效率的考虑,而且尽量减少数据通路上的逻辑,以达到低延时的目的。在高性能的先进封装中,物理层收发器则采用类似并行高速接口HBI/DDR的技术路线,结合高速SerDes中的均衡(Equalization)技术,实现最高32Gbps/pin的传输速率,通过最多64 bit数据位、前向同步时钟、数据有效、校正跟踪等信号实现数据通信,再配合低速Side Band信号实现通信中的信息交换。其中,0.25-0.5pJ/b的能耗目标,我们认为,将是工程设计中的重要挑战。

UCIe能否统一封装内互连技术?

UCIe的出现,标志着通过“先进封装+高速接口技术”实现“芯粒互连”已经成为“系统级大芯片开发”的主流方向,芯粒技术可以使大芯片达到更好性能,而且能降低成本和更早实现量产的目标。

此前,各厂商实现芯粒封装均采用独家定制技术,这给芯粒技术进一步普及带来了很高的成本和阻力,UCIe接口技术标准化以后,既为在芯粒技术上相对落后的厂商提供了技术路线,也可以让符合标准的由不同制造商生产的芯粒自由组合,从而为先进封装技术的繁荣普及奠定基础。

当然,UCIe产业联盟首创成员“从IP、芯片设计、晶圆制造、封测到应用”一应俱全,已经具备形成产业生态闭环的条件,这些产业巨头可利用定义标准的优势,进一步巩固其在先进集成电路技术方面的市场地位,拉大与竞争对手的差距。

值得注意的是,中国也在准备设立自己的Chiplet标准。2021年5月,中国计算机互连技术联盟(CCITA)在工信部立项了Chiplet标准,即《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多个芯片厂商合作展开标准制定工作。目前,该标准的第一版草案已制作完成,并在工信部中国电子技术标准化协会网站上,完成了挂网征求意见的相关流程。

中美两大组织都看到了为Chiplet建立接口标准的重要性,说明先进封装技术走到了一个关键点,标准制定向来是左右产业发展方向的路标。

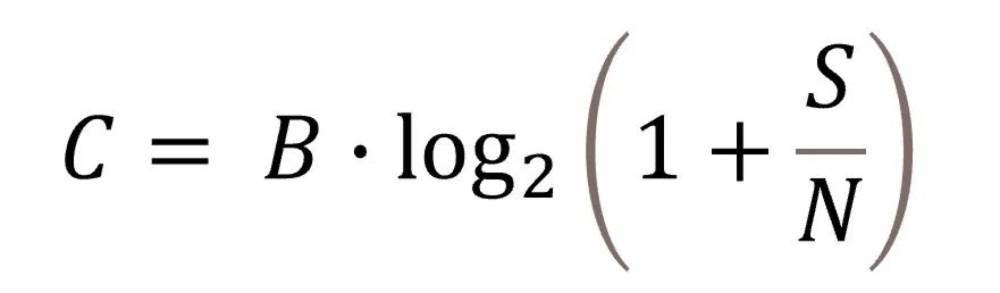

纵观多年的高速接口行业发展历程,一个新标准的提出,背后的商业目的各有不同,同一个技术难题,解决方案也各有利弊,但技术底层的物理极限,工程上还是必须遵循。我们认为,其中一个重要的物理极限就是“通信信道”。我们不妨回顾下通信教科书上的香农公式,

在高斯白噪声背景下的连续信道的容量:

B为信道带宽(Hz);S为信号功率(W);N为噪声功率(W)。

同时,这位信息论创始人香农告诉我们,信号的传输速率R(bps)不可超越这个信道容量C,所以要提高通信的传输速率需要提升信道容量,从公式看,提升信道容量主要的途径有两种,一个是增加信噪比S/N,一个是增加信道带宽B。例如,高速接口物理层设计中,为提高传输速率,引入FEC编码,本质上就是增加有效信噪比,从而有效提高信道容量限制;而业界有在采用的PAM4技术,本质上通过更高的调制阶数,只提高了信道利用率,但没有突破信道容量限制。先进封装技术,本质上直接改进了信道带宽,从而获得更高传输速率,UCIe就是针对这种新的通信信道提出的标准,我们认为这有其必要性。

从通信发展史来看,其实本质也是在解决“通信信道”问题。某种通信技术发展早期都会出现“春秋战国”的局面,各种标准各自为战,随着技术发展逐渐成熟,解决方案上特别是物理层技术上,会呈现“分久必合”的趋势。例如,高速串行通信技术出现后,出现过USB、SATA、HDMI、DP、PCIe等多种标准,但是,其本质都是采用SerDes技术解决一些相似的有线“信道”问题。随着SerDes技术日趋成熟,及不同产品之间相互融合,市场上会出现多协议高速SerDes(Multi-protocol 20G SerDes)这样的产品,兼容“信道”特征相似的USB 4.0、SATA 3.0、HDMI 2.1、PCIe 4.0等协议。无线通信领域也有类似规律,Wi-Fi、蓝牙、LoRa和5G等技术,针对了不同距离的“信道”而制定,才得以长期共存。因此,我们认为UCIe针对“封装上互联”这样全新“信道”的标准及其产品,有着相当的历史意义和生命力。

综上所述,对于UCIe标准的必要性和生命力,我们都有了更加清晰的认识。但我们更要深入思考的是,“UCIe能否实现一统封装互连市场”,这个话题还有待时间检验,通过实践给出答案。历史发展经验多次表明,越是开放互利的标准,越有机会。无论是国际UCIe标准还是国内Chiplet标准,芯耀辉都在积极布局,积累和贡献,期待与业界同仁多交流合作,共同推动中国后摩尔技术路线的发展!